Wat als uw harde schijf met uw gegevens mee kon denken? In plaats van alleen maar bestanden op te slaan, kunt u zich voorstellen dat de schijf informatie verwerkt en erop reageert, precies op de plek waar deze wordt bewaard. Dat is het principe achter in-memory computing - een groeiende verschuiving in architectuur waarbij logica dichter bij het geheugen wordt geplaatst om de efficiëntie te verhogen.

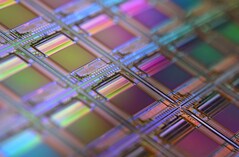

Onderzoekers van het Forschungszentrum Jülich en de Universiteit van Duisburg-Essen hebben nu een nieuw, op 2T1R memristor gebaseerd ontwerp gepresenteerd dat deze verschuiving zou kunnen ondersteunen en energie-efficiëntere AI en edge hardware mogelijk zou kunnen maken.

Gepubliceerd op arXivhet ontwerp integreert twee transistors en één memristor per cel, met stroomregeling bedoeld om sluipwegstromen te onderdrukken, een bekende uitdaging in memristor-arrays. In tegenstelling tot conventionele geheugens zet het voorgestelde ontwerp beide memristoruiteinden aan de grond wanneer ze niet actief zijn - een strategie die de signaalstabiliteit kan helpen verbeteren en lekkage kan helpen verminderen.

De architectuur is ontworpen om analoge vector-matrixvermenigvuldiging (VMM) te ondersteunen, een kernfunctie in machinaal leren, door de geleiding van de memristor te regelen met behulp van geïntegreerde DAC's, PWM-signalen en geregelde stroompaden. Er is met succes een 2×2 testarray geïmplementeerd met standaard 28 nm CMOS-technologie.

Door problemen met virtuele aarding en draadweerstand aan te pakken, beoogt de architectuur de voorspelbaarheid van de prestaties te verbeteren en het stroomverbruik te verminderen. Met compatibiliteit voor RISC-V besturing en digitale interfacing kan het 2T1R-ontwerp de basis leggen voor schaalbare neuromorfische chips, die snellere, compactere AI-versnelling direct in het geheugen mogelijk maken.

Uw harde schijf denkt misschien nog niet na, maar de architectuur achter die visie krijgt al vorm in silicium - een voorbode van een toekomst van snellere, in het geheugen geïntegreerde AI.

Voor volledige technische details en resultaten, zie de volledige arXiv preprint (PDF).

Bron(nen)

Top 10 Testrapporten

» Top 10 Multimedia Notebooks

» Top 10 Gaming-Notebooks

» Top 10 Budget Gaming Laptops

» Top 10 Lichtgewicht Gaming-Notebooks

» Top 10 Premium Office/Business-Notebooks

» Top 10 Budget Office/Business-Notebooks

» Top 10 Workstation-Laptops

» Top 10 Subnotebooks

» Top 10 Ultrabooks

» Top 10 Notebooks tot €300

» Top 10 Notebooks tot €500

» Top 10 Notebooks tot € 1.000De beste notebookbeeldschermen zoals getest door Notebookcheck

» De beste notebookbeeldschermen

» Top Windows Alternatieven voor de MacBook Pro 13

» Top Windows Alternatieven voor de MacBook Pro 15

» Top Windows alternatieven voor de MacBook 12 en Air

» Top 10 best verkopende notebooks op Amazon

» Top 10 Convertible Notebooks

» Top 10 Tablets

» Top 10 Tablets tot € 250

» Top 10 Smartphones

» Top 10 Phablets (>90cm²)

» Top 10 Camera Smartphones

» Top 10 Smartphones tot €500

» Top 10 best verkopende smartphones op Amazon